Introduction

The semiconductor industry is on the cusp of a significant transformation as Taiwan Semiconductor Manufacturing Company (TSMC) unveils its latest advancement in chip packaging technology, specifically designed for 3D-stacked processing units. This innovative approach promises to redefine the capabilities of electronic devices, enhance performance, and drive efficiency in an ever-evolving tech landscape.

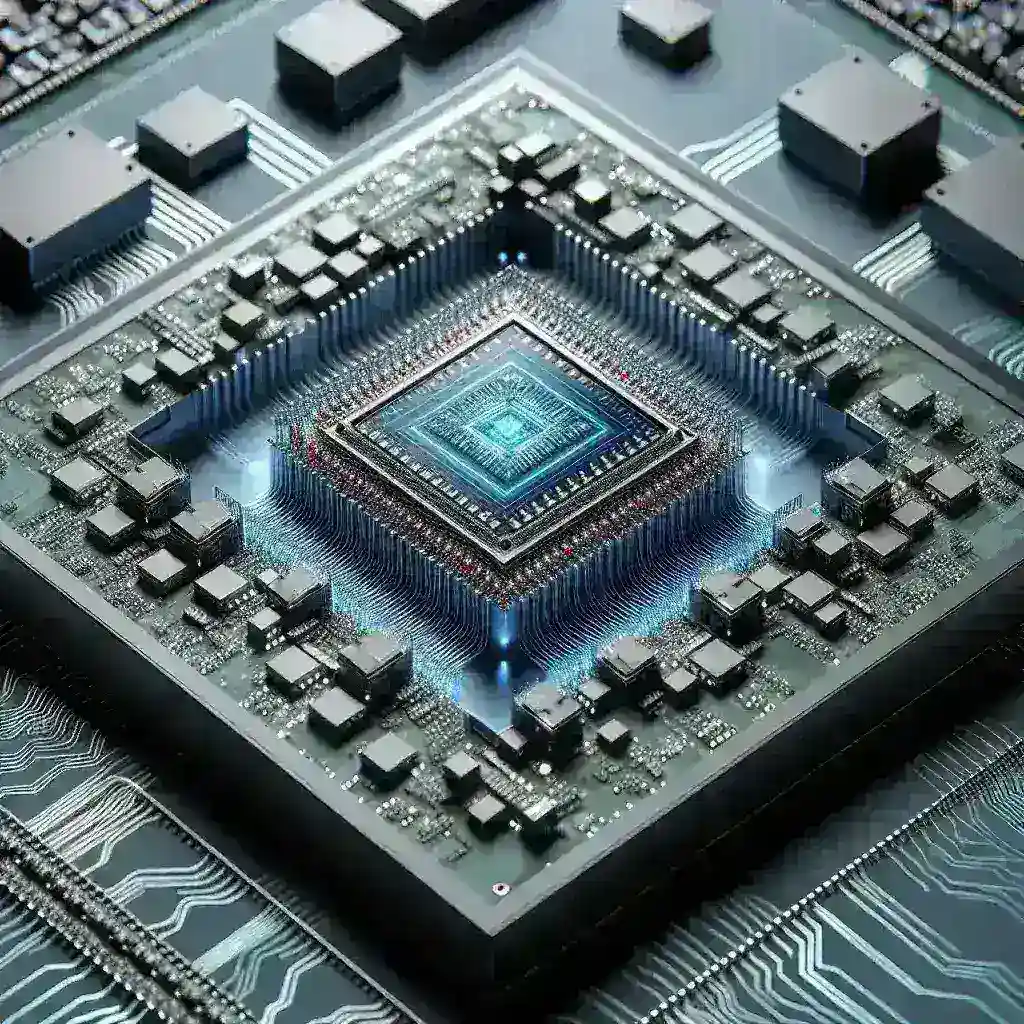

Understanding 3D-Stacked Processing Units

3D-stacked processing units are a revolutionary approach to chip design and manufacturing. Unlike traditional flat chip designs, 3D stacking involves layering multiple chips vertically, resulting in a compact and efficient design. This method not only conserves space but also reduces the distance data must travel between components, significantly improving speed and performance.

The Need for Advanced Packaging Technology

As consumer demands for faster, more efficient electronic devices grow, the limitations of conventional chip packaging methods have become increasingly apparent. Traditional packaging techniques often lead to challenges such as:

- Heat Dissipation: Increased power consumption generates heat that can affect performance and reliability.

- Space Constraints: The relentless push for smaller devices creates a need for more compact chip designs.

- Performance Bottlenecks: Longer data paths can introduce latency, hindering overall system performance.

TSMC’s Innovative Solution

In response to these challenges, TSMC has introduced a state-of-the-art packaging technology that leverages advanced materials and innovative design principles for 3D-stacked processing units. This technology aims to enhance the integration of multiple chips, allowing for improved performance and energy efficiency.

Key Features of TSMC’s New Technology

1. Enhanced Thermal Management: By utilizing advanced materials that effectively dissipate heat, TSMC’s new packaging technology ensures optimal operating temperatures for 3D-stacked units, contributing to longer device lifespans.

2. Increased Density: The ability to stack chips vertically allows for a significant reduction in footprint without sacrificing functionality, making it ideal for compact devices.

3. Improved Signal Integrity: TSMC’s technology minimizes the distance between stacked chips, enhancing data transfer rates and signal quality.

Implications for the Semiconductor Industry

TSMC’s introduction of this cutting-edge chip packaging technology is set to have far-reaching implications for the semiconductor industry. As the demand for high-performance computing continues to escalate, manufacturers will benefit from:

- Increased Production Efficiency: The streamlined design process associated with 3D stacking can lead to faster production cycles and reduced costs.

- Enhanced Device Performance: Devices utilizing this technology will offer superior performance, catering to high-end applications such as gaming, artificial intelligence, and data centers.

- A Competitive Edge: Companies adopting TSMC’s technology early will likely lead the market, attracting consumers seeking the latest advancements.

Historical Context and Future Predictions

The evolution of chip packaging has been a critical factor in the semiconductor industry’s growth. From early flat-pack designs to the introduction of ball grid arrays (BGAs) and multi-chip modules (MCMs), each advancement has paved the way for more efficient, powerful devices. TSMC’s new technology represents another leap forward in this ongoing journey.

Looking forward, we can expect to see:

- Wider Adoption: As more companies recognize the benefits of 3D-stacked processing units, adoption rates are likely to increase.

- Innovation in Applications: New applications and use cases will emerge as the technology becomes more prevalent, particularly in sectors like automotive, healthcare, and telecommunications.

- Global Influence: TSMC’s leadership in this area may influence global semiconductor manufacturing standards, setting benchmarks for quality and performance.

Pros and Cons of 3D Stacked Processing Units

As with any technology, the implementation of 3D-stacked processing units comes with its own set of advantages and challenges.

Advantages

- Space Efficiency: The vertical arrangement of chips conserves physical space, allowing for smaller form factors in devices.

- Performance Boost: Reduced latency and improved signal integrity result in faster processing speeds.

- Flexibility: The ability to mix and match different chips allows manufacturers to optimize performance for specific applications.

Challenges

- Complexity: Designing and manufacturing 3D-stacked units requires advanced technology and expertise.

- Cost: Initial investment in new materials and processes may be high, impacting short-term profitability.

- Thermal Management: While improved, managing heat in densely packed chips remains a critical challenge.

Conclusion

TSMC’s introduction of innovative chip packaging technology for 3D-stacked processing units marks a significant milestone in the semiconductor industry. By addressing the limitations of traditional packaging methods, TSMC is poised to drive the next wave of technological advancements, paving the way for faster, more efficient electronic devices that meet the growing demands of consumers and industries alike. As we move forward, the implications of this technology will undoubtedly shape the future landscape of electronics, influencing everything from device design to manufacturing standards.